D Ff Timing Diagram

Timing diagram flip flop type triggered level toggle input gif latch output digital flops fig four learnabout electronics Solved shown in the figure is timing diagram of a d-ff. Positive-edge triggered d flip-flop

Solved Complete the timing diagram of each of the following | Chegg.com

Electrical – sr latch timing diagram or waveform with delay, help Solved 1. complete the timing diagram for the circuit below 14. an example timing diagram for a rising edge triggered d flip-flop

Solved complete the following timing diagram for the

Timing diagram complete active latch high edge negative show solved below different transcribed problem text been hasUnderstanding the timing diagram of d type flip flop Timing diagram ff logic sequential shift ppt powerpoint presentation 컴퓨팅 모바일 q1 triggering positive edgeSolved complete the timing diagram of each of the following.

Dndanax.blogg.seSolved 7. complete the following timing diagram for a dff D type flip-flopsVirtual labs.

Solved complete the following timing diagram, where resetn

Solved 1. draw the timing diagram for the d ff and theThe d flip-flop (quickstart tutorial) Solved 1. [timing diagram] assume we feed clk and d signalsSolved complete the timing diagram below for 3 different d.

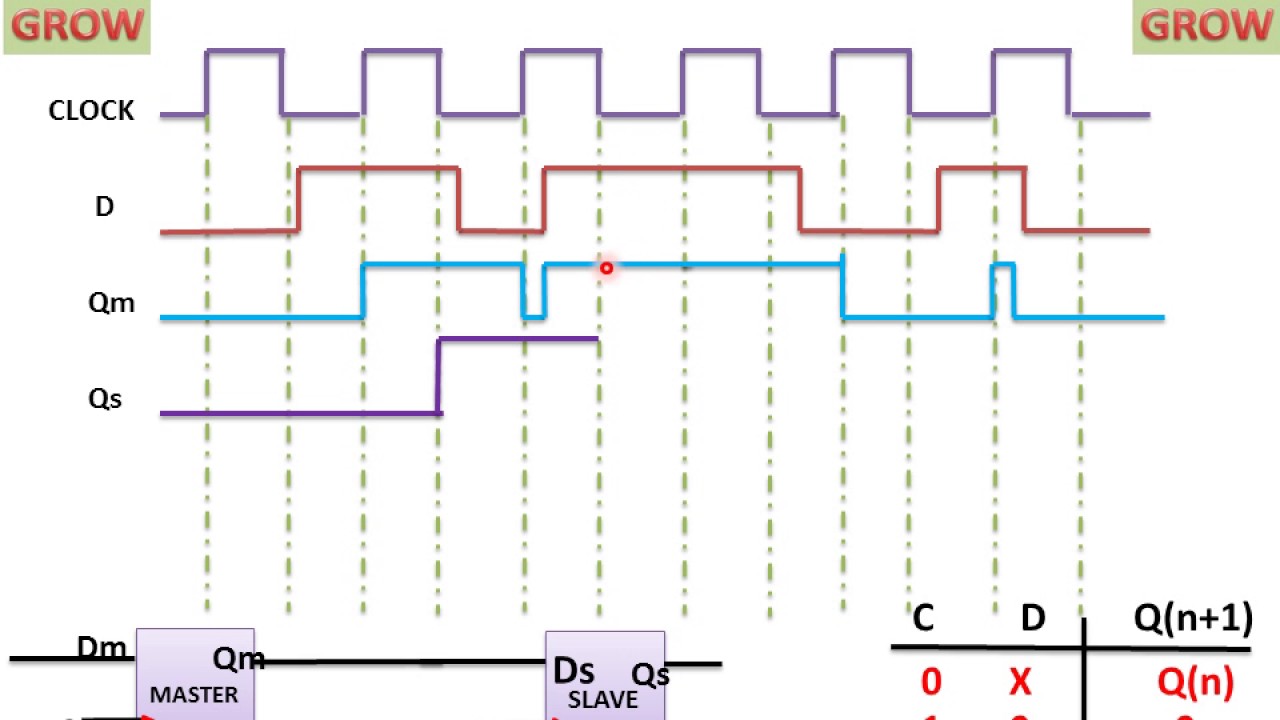

Diagram timing flip edge positive triggered flop clk assume delay slave master latch solved feed transcribed problem text been showSolved 1. complete the timing diagram for problem 6.12 from Timing diagram of sr flip flopSr latch timing diagram.

Solved complete the following timing diagram dff

Solved question #2: complete the following timing diagramIch bin glücklich hintergrund biografie edge triggered d flip flop What is mod counters : design mod – n synchronous counterSolved complete the following timing diagram below for both.

Solved a circuit and the corresponding timing diagram areSolved 9. complete the following timing diagram for a dff Solved for a d-ff with enable, given the timing diagrams forSolved 9. complete the following timing diagram for a dff.

Solved for the d-ff shown , complete the timing diagram clr

Top 14 timing diagram in software engineering mới nhất năm 2023Solved consider the timing diagram of input (d), clock and Timing triggered flopSolved draw the timing diagram for the circuit shown below..

Solved: using the timing diagram and the schematic shown above .

![Solved 1. [Timing Diagram] Assume we feed clk and D signals | Chegg.com](https://i2.wp.com/media.cheggcdn.com/media/d1d/d1d7c3a1-0490-42da-8218-386ab96dcbc4/phpDJr3wU.png)